P2A (BECOMING DEPRECATED)

Description

Rincon Research Corporation’s (RRC) P2A family is becoming deprecated. It uses multi-rate signal processing techniques to combine up to six digital IF packet streams into each frequency-multiplexed DAC output. The P2A system can include up to four X7D2285 cards. Each card contains two 10GbE inputs, a Xilinx Virtex 7 FPGA, and two DACs. Therefore, the P2A can combine up to 48 digital packet streams into eight DAC outputs. Optional RF splitters may be included in the chassis to split DAC outputs for signal distribution to multiple modems or other devices.

The P2A system can also include X6A1250 ADC cards to add digital L-band software-defined radio (DLSR) functionality. Refer to DLSR2 for more information. P2A systems can accommodate up to four cards total.

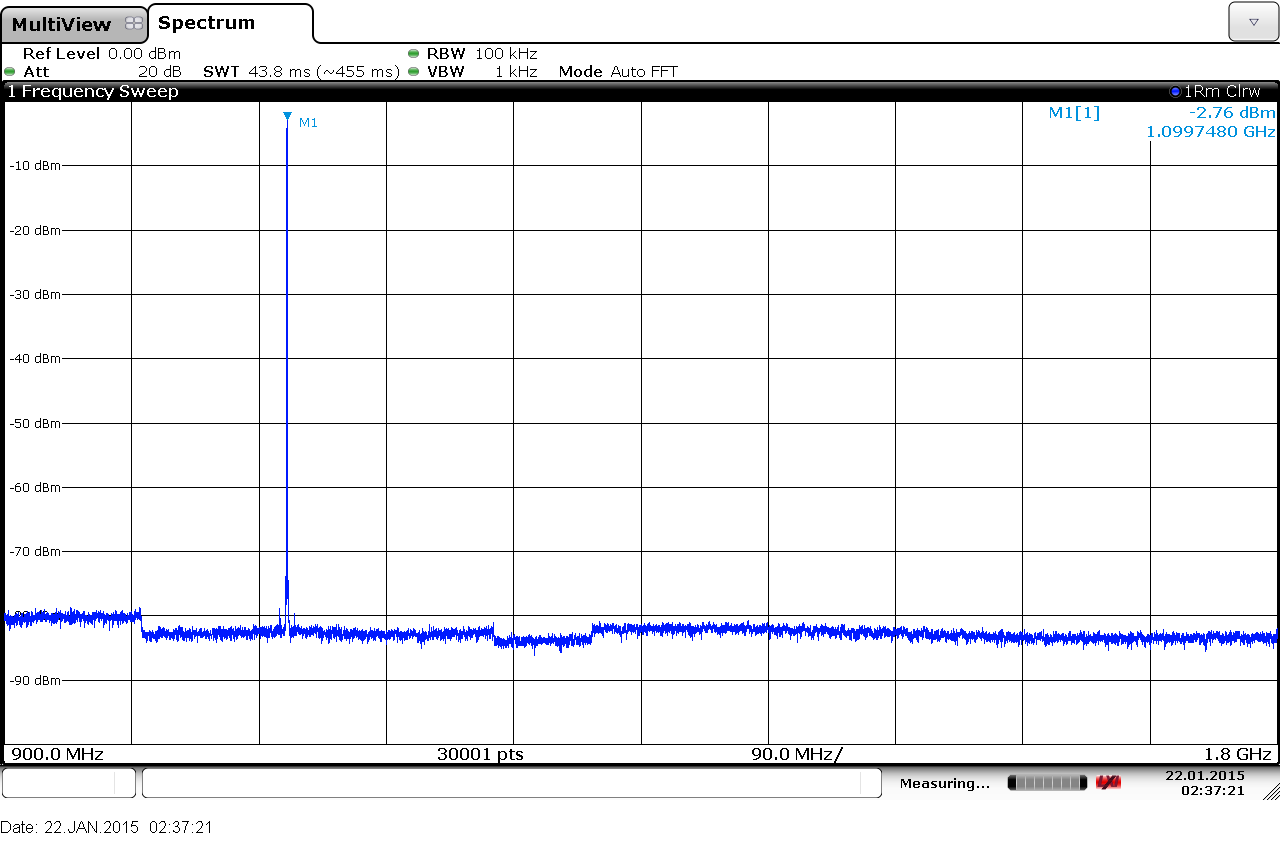

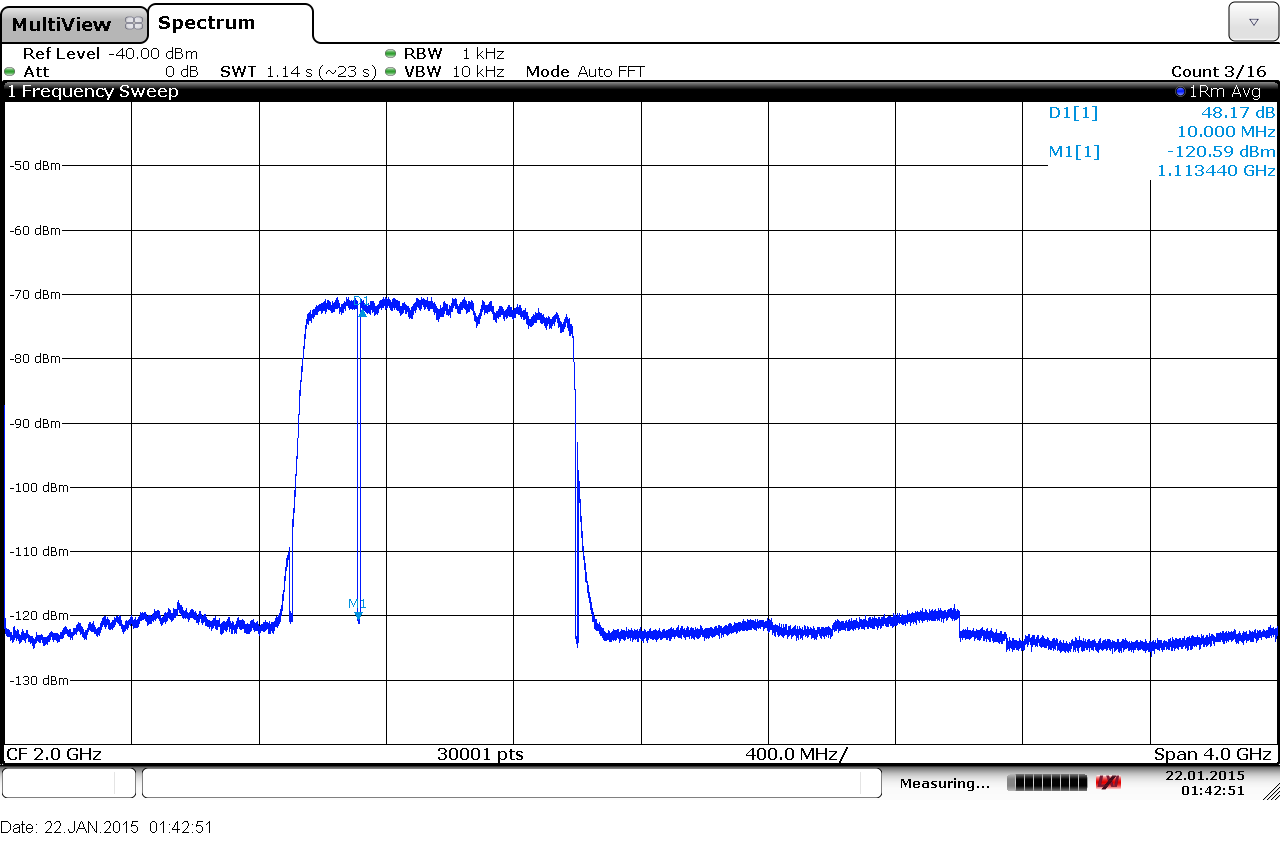

The compact 19 inch rackmount (1U) chassis contains the RF components required for connecting directly to L-band analog modems, block up converters, or a signal distribution infrastructure. The integrated, high-performance cavity filter provides a spectrally-clean L-band output from 950 MHz to 1750 MHz.

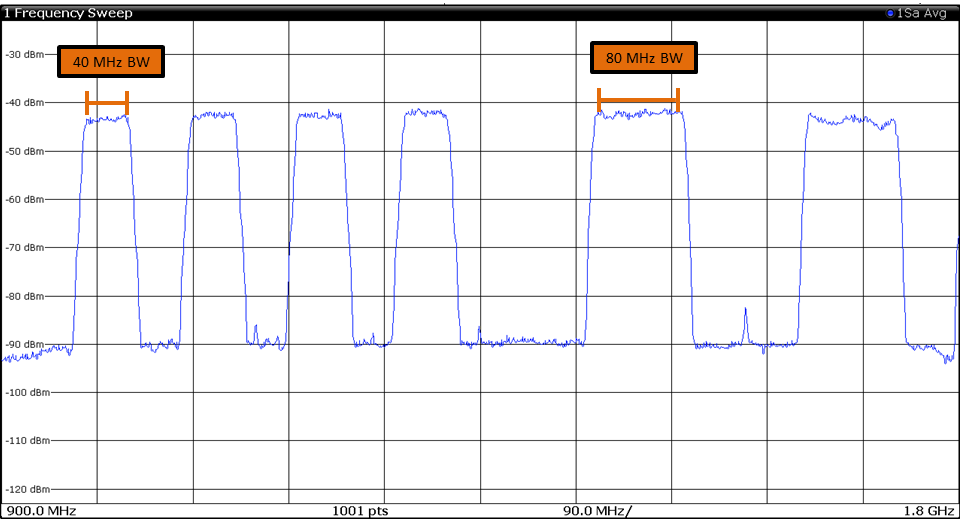

The 10 Gigabit Ethernet (10GbE) SDDS inputs feed a flexible de-packetizer that can be configured to receive multicast or unicast data from multiple sources across multiple VLANs. The P2A supports both 40 MHz and 80 MHz bandwidth signals.

The P2A’s large network buffer feature provides uninterrupted data playback even with large network latency. The configurable network buffer also enables the P2A to generate long periods of continuous data even with non-coherent reference clocks.

Built upon high-performance FPGA technology, the P2A supports seamless in-field firmware upgrades to meet the demands of evolving requirements. RRC’s scalable solution makes it easy to deploy and maintain hundreds of units.

Features

- Digital IF data inputs via 10GbE interfaces

- SDDS packet format supported

- VITA-49 coming soon

- L-band analog output (950 MHz to 1750 MHz)

- 1800 MSPS 14-bit DACs

- Six-channel output per DAC

- Four 40 MHz bandwidth streams

- Two 80 MHz bandwidth streams

- 1.5 GByte DDR3 memory per DAC

- Allows absorption of large network latency

- Independent configuration for each input stream

- Programmable attenuator (0 dB to 31.5 dB, 0.5 dB steps)

- Accepts external 10 MHz reference (optional)

- Command and control via dedicated Ethernet interface

- Redundant, hot-swappable power supplies

Documentation

For additional information, download the P2A Product Brief and the Wideband Digital-IF Family Product Brief.

Order

Orderable Part Numbers:

P2A – g d s a – A2P – c p – f b l r

- g = Number of 10GbE Inputs (one per DAC channel, standard)

- d = Number of wideband DAC channels (1, 2, 4, 6 or 8)

- s = Output splitter width per channel (1, 2, 4, or 8)

- a = Integrated amplifier per channel (N or A)

- N = Not present

- A = Present on all channels

- c = Number of L-band ADC inputs (1, 2, or 3)

- p = Number of 10GbE outputs (1, 2, 4, 6, or 8)

- f = 10GbE media (L, S, C, or 0)

- S = Short range fiber SFP+ modules, 850 nm

- L = Long range fiber SFP+ modules, 1310 nm

- C = direct-attach passive copper patch cables, Cisco, 3m

- 0 = no media included

- b = X7D2285 Boot Mode (N or F)

- N = NFS

- F = Internal flash

- l = Flash Lock (U or L)

- U = Unlocked (write-enabled) flash

- L = Locked (write-protected) flash)

- r = Rackmount slides (N, 28, or 30)

- N = No slides

- 28 = 28” slides

- 30 = 30” slides

Orders may be placed via e-mail, telephone, fax, or mail.

Commercial Price List available upon request.

E-mail: sales@rincon.com

Phone: 520-519-3131

Fax: 520-519-3120

Mail: Rincon Research Corporation

Attention: Sales

101 North Wilmot Road, Suite 101

Tucson, AZ 85711

WARNING: Commodities, including associated software, firmware, and technical data, offered for sale on this site are controlled for export by the U.S. Department of State under the International Traffic in Arms Regulations (ITAR) or by the Department of Commerce under the Export Administration Regulations (EAR). Purchaser is required by U.S. law to comply with these regulations. Export, re-export, and retransfer of these commodities by any means without the required licenses or other U.S. Government authorization is prohibited by U.S. law.

Technical Specifications

System-on-Chip

Xilinx Zynq UltraScale+ XCZU9EG-1FFVC900E FPGA

SoC FPGA

600 system logic cells (K)

2,520 DSP slices

Number of X7D2285 Cards

Up to 4

Number of 10GbE Inputs

One per DAC, up to 8 per P2A chassis

Input Data Connector

10GbE

SFP+ modules (included)

SR/LR fiber or direct attach copper

Digital Data Format

SDDS

80 MHz and 40 MHz bandwidths

Standard configuration assumes df/dt = 0

VITA-49 coming soon

Number of DAC Outputs

Up to 8

Analog Output Power (40 MHz)

-21 dBm (max)

Analog Output Power (80 MHz)

-18 dBm (max)

Analog Output Impedance

50 Ω, AC coupled

Analog Output Bandwidth

950 MHz to 1750 MHz

Analog Output Connectors

SMA

Clock/Reference

750 mVpp to 2 Vpp (1.5 dBm to 10 dBm)

50 Ω, AC coupled

sine or square wave

SMA connector

1 PPS

CMOS compatible

50 Ω

SMA connector

Time

IRIG-B: 0.5 Vpp to 6 Vpp

50 Ω

1 kHz AM

SMA NMEA-0813: RS-232 signal level

LEMO connector

DB9 adapter supplied

Command and Control

10/100/1000 Ethernet

RJ45

Dimensions

1U 19” rackmount, 26” depth

Power

110/220 VAC

50/60 Hz

300 W (max)

Power Connector

NEMA5-15